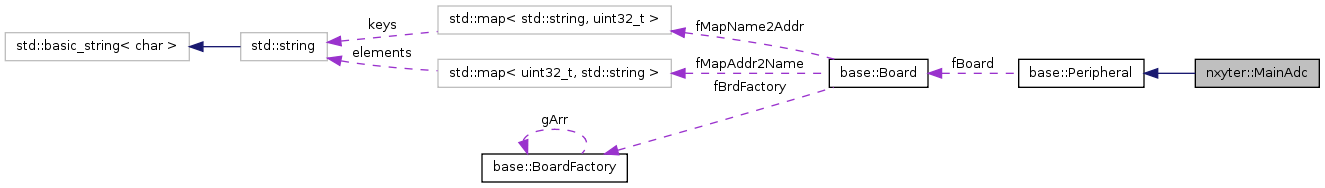

Represents the full interface to a AD9228/AD9219 ADC. More...

#include <MainAdc.h>

Public Types | |

| enum | adcRegs { kReg_chip_port_config = 0x00, kReg_chip_id = 0x01, kReg_chip_grade = 0x02, kReg_device_index_A = 0x05, kReg_modes = 0x08, kReg_clock = 0x09, kReg_test_io = 0x0d, kReg_output_mode = 0x14, kReg_output_adjust = 0x15, kReg_output_phase = 0x16, kReg_user_patt1_lsb = 0x19, kReg_user_patt1_msb = 0x1a, kReg_user_patt2_lsb = 0x1b, kReg_user_patt2_msb = 0x1c, kReg_serial_control = 0x21, kReg_serial_ch_stat = 0x22, kReg_device_update = 0xff } |

Names for ADC Registers. More... | |

Public Member Functions | |

| MainAdc () | |

| Default constructor. | |

| MainAdc (base::Board *board, int port, bool mode4nx=false) | |

| Constructor with full addressing path information. | |

| virtual | ~MainAdc () |

| bool | isSPI () const |

| int | setRegister (uint8_t reg, uint8_t val, bool veri=false) |

| Write to ADC device register with optional readback verification. | |

| int | getRegister (uint8_t reg, uint8_t &val) |

| Read from ADC device register. | |

| int | setTestMode (int ch, uint8_t mode) |

| Setup test pattern mode mode for ADC channel ch. | |

| int | setUserPattern (uint16_t pat) |

| Setup user test pattern pat for all ADC channels. | |

| int | probe () |

| Probe whether an ADC exists. | |

| int | setToDefault () |

| Set the ADC registers to default values suitable for data taking. | |

| void | printRegisters (std::ostream &os) |

| Read ADC registers and print to stream os. | |

| int | setChannelMux (int nxnum, uint32_t val) |

| Setup association of nXYTER chips and ADC channels. | |

| int | setChannelLatency (int nxnum, uint32_t val) |

| Set delay of ADC data relative to nXYTER data. | |

| int | getChannelLatency (int nxnum, uint32_t &val) |

| Returns delay of ADC data relative to nXYTER data. | |

| int | setClockDelay (uint32_t val) |

| Set the relative phase between the nXYTER and the ADC clock. | |

| int | setClockDelaySrInit (uint32_t val) |

| Set nXYTER to ADC clock phase, 'SR_INIT' part. | |

| int | getClockDelaySrInit (uint32_t &val) |

| Returns 'SR_INIT' part of nXYTER to ADC clock phase adjust. | |

| int | setClockDelayBufg (uint32_t val) |

| Set nXYTER to ADC clock phase, 'BUFG' part. | |

| int | getClockDelayBufg (uint32_t &val) |

| Returns 'BUFG' part of nXYTER to ADC clock phase adjust. | |

| int | getAdcDirect (int num, uint32_t &val) |

| Direct access to ADC values. | |

| base::Board & | board () |

Return reference to roc::Board which hosts the Peripheral. | |

| base::Board * | getBoard () const |

Returns pointer to the roc::Board which hosts the Peripheral. | |

Static Public Member Functions | |

| static void | calcClockDelayRegs (uint32_t delay, uint32_t &sr_init, uint32_t &bufg_select) |

| Calculates registers values for specified ADC clock delay. | |

| static uint32_t | findClockDelay (uint32_t sr_init, uint32_t bufg_select) |

| Finds clock delay value, which is correspond to specified regs. Returns 0xffff if fails. | |

| static const char * | registerName (int reg) |

| Returns name for register reg (or "" if undefined). | |

| static void | addAddrMap (base::Board *board) |

Protected Attributes | |

| int | fUseSPI |

| indicate that SPI->I2C interface for SysCore3 should be used | |

| int | fPort |

| the port number | |

| bool | fMode4nx |

| 4nx mode selector | |

| base::Board * | fBoard |

| board pointer | |

Related Functions | |

(Note that these are not member functions.) | |

| std::ostream & | operator<< (std::ostream &os, nxyter::MainAdc &obj) |

| ostream insertion for nxyter::MainAdc | |

Detailed Description

Represents the full interface to a AD9228/AD9219 ADC.

This class provides the access to the ROC and SMI interface parts of the main data ADC used on the FEB's. It holds the full address information but no further context.

Definition at line 17 of file MainAdc.h.

Member Enumeration Documentation

Names for ADC Registers.

- Enumerator:

Constructor & Destructor Documentation

| nxyter::MainAdc::MainAdc | ( | ) |

Default constructor.

Definition at line 29 of file MainAdc.cxx.

| nxyter::MainAdc::MainAdc | ( | base::Board * | board, | |

| int | port, | |||

| bool | mode4nx = false | |||

| ) |

Constructor with full addressing path information.

Sets up MainAdc object with full addressing information

- Parameters:

-

board ROC board pointer port the ROC port mode4nx if trueconfigure for FEB4nx class FEBs

- Note:

- For FEB1nx class or glo_feb_feb2nx FEBs the control and data interface is on the same port. For FEB4nx class FEBs the port is always 0 (CON19), but the control interface is on port 0 (CON19) while the data interface is at port 1 (CON20). Therefore the mode4nx flag is needed to always have a complete addressing information available in the object.

Definition at line 54 of file MainAdc.cxx.

References fUseSPI, and base::Board::is_SPI_I2C().

| nxyter::MainAdc::~MainAdc | ( | ) | [virtual] |

Definition at line 66 of file MainAdc.cxx.

Member Function Documentation

| void nxyter::MainAdc::addAddrMap | ( | base::Board * | board | ) | [static] |

Definition at line 740 of file MainAdc.cxx.

References base::Board::addRegAddrMapping(), base::Board::is_SPI_I2C(), ROC_NX_ADC_ADDR, ROC_NX_ADC_ADDR2, ROC_NX_ADC_ANSWER, ROC_NX_ADC_ANSWER2, ROC_NX_ADC_DIRECT_1a, ROC_NX_ADC_DIRECT_1b, ROC_NX_ADC_DIRECT_1c, ROC_NX_ADC_DIRECT_1d, ROC_NX_ADC_DIRECT_2a, ROC_NX_ADC_DIRECT_2b, ROC_NX_ADC_DIRECT_2c, ROC_NX_ADC_DIRECT_2d, ROC_NX_ADC_LATENCY1, ROC_NX_ADC_LATENCY2, ROC_NX_ADC_LATENCY3, ROC_NX_ADC_LATENCY4, ROC_NX_ADC_PORT_SELECT1, ROC_NX_ADC_PORT_SELECT2, ROC_NX_ADC_PORT_SELECT3, ROC_NX_ADC_PORT_SELECT4, ROC_NX_ADC_REG, ROC_NX_ADC_REG2, ROC_NX_BUFG_SELECT, ROC_NX_BUFG_SELECT2, ROC_NX_SR_INIT, ROC_NX_SR_INIT2, ROC_SPI_COMMAND, ROC_SPI_MASTER_STATUS, ROC_SPI_RXDATA, ROC_SPI_TRANSMIT, and ROC_SPI_TXDATA.

Referenced by cmd_board(), and main().

| base::Board & base::Peripheral::board | ( | ) | [inherited] |

Return reference to roc::Board which hosts the Peripheral.

- Exceptions:

-

std::runtime_error if board pointer not initialized or 0.

Definition at line 30 of file Peripheral.cxx.

References base::Peripheral::fBoard.

Referenced by nxyter::RocNx::fireTestPulse(), getAdcDirect(), nxyter::NxChip::getChannelDelay(), getChannelLatency(), getClockDelayBufg(), getClockDelaySrInit(), base::Gpio::getConfig(), nxyter::RocNx::getDataDebug(), nxyter::RocNx::getFifoEmpty(), nxyter::RocNx::getFifoFull(), nxyter::RocNx::getNxActive(), roc::I2cDevice::getRegister(), getRegister(), roc::I2cDevice::getRegister16(), base::Gpio::getSyncBaud(), base::Gpio::getSyncScale(), nxyter::FebBase::initRoc(), nxyter::FebBase::resetNxI2cBus(), nxyter::FebBase::resetNxI2cRegister(), nxyter::RocNx::resetRocNxTs(), nxyter::NxChip::setChannelDelay(), setChannelLatency(), setChannelMux(), setClockDelay(), setClockDelayBufg(), setClockDelaySrInit(), base::Gpio::setConfig(), nxyter::RocNx::setDebugMode(), nxyter::RocNx::setLTSDelay(), nxyter::RocNx::setNxActive(), nxyter::NxChip::setNxNumber(), nxyter::RocNx::setParityCheck(), roc::I2cDevice::setRegister(), setRegister(), roc::I2cDevice::setRegisterVerify(), base::Gpio::setSyncBaud(), base::Gpio::setSyncScale(), and nxyter::RocNx::setToDefault().

| void nxyter::MainAdc::calcClockDelayRegs | ( | uint32_t | delay, | |

| uint32_t & | sr_init, | |||

| uint32_t & | bufg_select | |||

| ) | [static] |

Calculates registers values for specified ADC clock delay.

Definition at line 525 of file MainAdc.cxx.

Referenced by findClockDelay(), and setClockDelay().

| uint32_t nxyter::MainAdc::findClockDelay | ( | uint32_t | sr_init, | |

| uint32_t | bufg_select | |||

| ) | [static] |

Finds clock delay value, which is correspond to specified regs. Returns 0xffff if fails.

Definition at line 543 of file MainAdc.cxx.

References calcClockDelayRegs(), and delay().

Referenced by AdcWidget::displayClockDelay().

| int nxyter::MainAdc::getAdcDirect | ( | int | num, | |

| uint32_t & | val | |||

| ) |

Direct access to ADC values.

In normal operation the ADC values are only inspected when a nXYTER data valid is processed, in this case the ADC reading is placed as part of the hit message into the data stream. For tests it is sometimes desireable to directly read the ADC values. This methods provides this access, and returns the current ADC value for channel num.

Note that the ADC values are updated at 32 MHz. Note also, that in quiecent state the nXYTER tends to produce a reading close to ADC midrange, completely independent of the nXYTER baseline settings.

- Parameters:

-

num ADC channel number (0-3) val ADC data (12 bit)

- Returns:

- see roc::Board get/put/oper return codes, or -1 if num out-of-range

Definition at line 664 of file MainAdc.cxx.

References ADC_PORT_A, ADC_PORT_B, ADC_PORT_C, ADC_PORT_D, base::Peripheral::board(), CON19, CON20, fMode4nx, fPort, base::Board::get(), isSPI(), ROC_NX_ADC_DIRECT_1a, ROC_NX_ADC_DIRECT_1b, ROC_NX_ADC_DIRECT_1c, ROC_NX_ADC_DIRECT_1d, ROC_NX_ADC_DIRECT_2a, ROC_NX_ADC_DIRECT_2b, ROC_NX_ADC_DIRECT_2c, and ROC_NX_ADC_DIRECT_2d.

Referenced by cmd_getadcdirect(), and nxyter::FebUtil::testMainAdcDataPath().

| base::Board* base::Peripheral::getBoard | ( | ) | const [inline, inherited] |

Returns pointer to the roc::Board which hosts the Peripheral.

Note: normally using board() is more convenient.

Definition at line 38 of file Peripheral.h.

References base::Peripheral::fBoard.

Referenced by nxyter::FebUtil::acquireTestTriggerData(), nxyter::NxChip::activate(), nxyter::FebBase::addNxChip(), nxyter::NxChip::deactivate(), nxyter::NxChip::isactive(), and nxyter::QuickDaq::QuickDaq().

| int nxyter::MainAdc::getChannelLatency | ( | int | nxnum, | |

| uint32_t & | val | |||

| ) |

Returns delay of ADC data relative to nXYTER data.

- Parameters:

-

nxnum see nXYTER number val delay of ADC data relative to nXYTER data in 250MHz clocks

- Returns:

- see roc::Board get/put/oper return codes, or -1 if nxnum out-of-range

- See also:

- getChannelLatency()

Definition at line 469 of file MainAdc.cxx.

References base::Peripheral::board(), base::Board::get(), isSPI(), ROC_NX_ADC_LATENCY1, ROC_NX_ADC_LATENCY2, ROC_NX_ADC_LATENCY3, and ROC_NX_ADC_LATENCY4.

Referenced by cmd_scanadclat().

| int nxyter::MainAdc::getClockDelayBufg | ( | uint32_t & | val | ) |

Returns 'BUFG' part of nXYTER to ADC clock phase adjust.

- See also:

- setClockDelayBufg()

Definition at line 636 of file MainAdc.cxx.

References base::Peripheral::board(), CON19, fPort, base::Board::get(), isSPI(), ROC_NX_BUFG_SELECT, and ROC_NX_BUFG_SELECT2.

Referenced by cmd_scanadclat(), and AdcWidget::getOnlyDelayRegs().

| int nxyter::MainAdc::getClockDelaySrInit | ( | uint32_t & | val | ) |

Returns 'SR_INIT' part of nXYTER to ADC clock phase adjust.

- Parameters:

-

val initial shift register setting (16 bit)

- Returns:

- see roc::Board get/put/oper return codes

- See also:

- setClockDelaySrInit()

Definition at line 592 of file MainAdc.cxx.

References base::Peripheral::board(), CON19, fPort, base::Board::get(), isSPI(), ROC_NX_SR_INIT, and ROC_NX_SR_INIT2.

Referenced by cmd_scanadclat(), and AdcWidget::getOnlyDelayRegs().

| int nxyter::MainAdc::getRegister | ( | uint8_t | reg, | |

| uint8_t & | val | |||

| ) |

Read from ADC device register.

Reads an 8bit value from device register reg.

- Parameters:

-

reg device register number val value

- Returns:

- see roc::Board get/put/oper return codes

- See also:

- setRegister()

Definition at line 155 of file MainAdc.cxx.

References base::Peripheral::board(), fPort, isSPI(), base::Board::kOperBusErr, base::Board::operErrBuild(), base::Board::operGen(), base::Board::operPG(), ROC_NX_ADC_ADDR, ROC_NX_ADC_ADDR2, ROC_NX_ADC_ANSWER, and ROC_NX_ADC_ANSWER2.

Referenced by AdcWidget::getSubConfig(), printRegisters(), probe(), and setTestMode().

| bool nxyter::MainAdc::isSPI | ( | ) | const [inline] |

Definition at line 28 of file MainAdc.h.

References fUseSPI.

Referenced by getAdcDirect(), getChannelLatency(), getClockDelayBufg(), getClockDelaySrInit(), getRegister(), setChannelLatency(), setChannelMux(), setClockDelayBufg(), setClockDelaySrInit(), and setRegister().

| void nxyter::MainAdc::printRegisters | ( | std::ostream & | os | ) |

Read ADC registers and print to stream os.

Produces a nicely formatted listing of all ADC settings with the value given in hex, decimal and also binary representation. An ADC with default settings setup by setToDefault() will produce

Reg( 0) chip_port_config: 0x18 24 0 0 0 1 1 0 0 0 Reg( 1) chip_id : 0x02 2 0 0 0 0 0 0 1 0 Reg( 2) chip_grade : 0x11 17 0 0 0 1 0 0 0 1 Reg( 5) device_index_A : 0x0f 15 0 0 0 0 1 1 1 1 Reg( 8) modes : 0x00 0 0 0 0 0 0 0 0 0 Reg( 9) clock : 0x01 1 0 0 0 0 0 0 0 1 Reg(13) test_io : 0x00 0 0 0 0 0 0 0 0 0 Reg(20) output_mode : 0x00 0 0 0 0 0 0 0 0 0 Reg(21) output_adjust : 0x00 0 0 0 0 0 0 0 0 0 Reg(22) output_phase : 0x03 3 0 0 0 0 0 0 1 1 Reg(25) user_patt1_lsb : 0x00 0 0 0 0 0 0 0 0 0 Reg(26) user_patt1_msb : 0x00 0 0 0 0 0 0 0 0 0 Reg(27) user_patt2_lsb : 0x00 0 0 0 0 0 0 0 0 0 Reg(28) user_patt2_msb : 0x00 0 0 0 0 0 0 0 0 0 Reg(33) serial_control : 0x03 3 0 0 0 0 0 0 1 1 Reg(34) serial_ch_stat : 0x00 0 0 0 0 0 0 0 0 0

Definition at line 381 of file MainAdc.cxx.

References getRegister(), and registerName().

Referenced by cmd_printadc(), operator<<(), and nxyter::FebBase::printRegisters().

| int nxyter::MainAdc::probe | ( | ) |

Probe whether an ADC exists.

This method tries to test in a reliable but as much as possible non-intrusive way whether an ADC chip is accessible under the port setup for the object. The probe procedure uses the four user pattern registers of the ADC and performs four steps

- read these registers

- write distinct values into these registers

- read back and check the distinct values

- restore the initial settings (saved in first step)

The method aborts and returns with a non-zero return code when any of the above operation or tests fail. In case of success the ADC chip is in the same state as before.

The probe is mostly non-intrusive because only registers used in test modes are used, and should therefore not disput normal operation.

- Returns:

- 0 on success and non-zero if any step fails. See roc::Board get/put/oper return codes for details. The index refers to the 16 get and set operations and thus allows to precisely pinpoint at what point the probe aborted.

Definition at line 271 of file MainAdc.cxx.

References getRegister(), base::Board::kOperVerifyErr, kReg_user_patt2_msb, base::Board::operErrBuild(), and setRegister().

Referenced by nxyter::FebBase::discoverFebs(), nxyter::FebUtil::probe(), and nxyter::FebUtil::testMainAdcControlPath().

| const char * nxyter::MainAdc::registerName | ( | int | reg | ) | [static] |

Returns name for register reg (or "" if undefined).

Definition at line 695 of file MainAdc.cxx.

Referenced by AdcWidget::AdcWidget(), and printRegisters().

| int nxyter::MainAdc::setChannelLatency | ( | int | nxnum, | |

| uint32_t | val | |||

| ) |

Set delay of ADC data relative to nXYTER data.

- Parameters:

-

nxnum see nXYTER number val delay of ADC data relative to nXYTER data in 250MHz clocks

- Returns:

- see roc::Board get/put/oper return codes, or -1 if nxnum out-of-range

- See also:

- getChannelLatency()

Definition at line 445 of file MainAdc.cxx.

References base::Peripheral::board(), isSPI(), base::Board::put(), ROC_NX_ADC_LATENCY1, ROC_NX_ADC_LATENCY2, ROC_NX_ADC_LATENCY3, and ROC_NX_ADC_LATENCY4.

Referenced by cmd_scanadclat().

| int nxyter::MainAdc::setChannelMux | ( | int | nxnum, | |

| uint32_t | val | |||

| ) |

Setup association of nXYTER chips and ADC channels.

The ROC can serve one or two FEBs, each with 4 channel ADC, and a total or four nXYTER chips. An ADC channel mux allows to associate every nXYTER data channel with any of the 4 possible ADC data channels of the associated port. This method controls the setting of this multiplexer.

- Parameters:

-

nxnum see nXYTER number val ADC channel. Only 2 LSB are used, valid values are - 0 use data from connector pin A17/B17

- 1 use data from connector pin A18/B18

- 2 use data from connector pin A20/B20

- 3 use data from connector pin A21/B21

- Returns:

- see roc::Board get/put/oper return codes, or -1 if nxnum out-of-range

- Note:

- The ADC data for nxnum = 0 and 1 is taken from port 0 (CON19) for FEB1nx class and FEB2nx class FEBs and from port 1 (CON20) for FEB4nx class FEBs. The ADC data for nxnum = 2 and 3 is always taken from port 1 (CON20).

Definition at line 421 of file MainAdc.cxx.

References base::Peripheral::board(), isSPI(), base::Board::put(), ROC_NX_ADC_PORT_SELECT1, ROC_NX_ADC_PORT_SELECT2, ROC_NX_ADC_PORT_SELECT3, and ROC_NX_ADC_PORT_SELECT4.

Referenced by nxyter::FebBase::initRoc().

| int nxyter::MainAdc::setClockDelay | ( | uint32_t | delay | ) |

Set the relative phase between the nXYTER and the ADC clock.

The ADC clock can be shifted relative to the nXYTER clock to adjust the proper data sampling timing on the FEB. The clock shift is implemented on the ROC in a two stage fashion, leading to two internal setup parameters. This method takes a desired delay in units of ns as input, calculates these parameters, and calls the low level methods setClockDelaySrInit() and setClockDelayBufg() to transmit them to the ROC.

- Note:

- The mapping of delay to the hardware settings is done such that a larger value of delay will cause a later sampling of the nXYTER data by the ADC. This way the time direction used by this method and by setChannelLatency() is the same.

- Parameters:

-

delay desired delay on units of 1 ns

- Returns:

- see roc::Board get/put/oper return codes

Definition at line 503 of file MainAdc.cxx.

References base::Peripheral::board(), calcClockDelayRegs(), base::Board::Debug(), base::Board::operErrBuild(), setClockDelayBufg(), and setClockDelaySrInit().

Referenced by cmd_scanadclat(), cmd_setadcclock(), AdcWidget::setClockDelay(), and AdcWidget::setSubToDefault().

| int nxyter::MainAdc::setClockDelayBufg | ( | uint32_t | val | ) |

Set nXYTER to ADC clock phase, 'BUFG' part.

Low level method to setup one of of two parameters controling the relative phase between the nXYTER and the ADC clock. At the user level always call setClockDelay().

The 'BUFG' setting determines whether the 250 MHz clock is used directly (val = 0) or a clock shifted by 90 degree is used (val = 1). This changes the relative clock phase between nXYTER and ADC on the FEB by 1 ns.

- Parameters:

-

val new clock phase mux setting (1 bit)

- Returns:

- see roc::Board get/put/oper return codes

- See also:

- getClockDelayBufg()

Definition at line 619 of file MainAdc.cxx.

References base::Peripheral::board(), CON19, fPort, isSPI(), base::Board::put(), ROC_NX_BUFG_SELECT, and ROC_NX_BUFG_SELECT2.

Referenced by cmd_scanadclat(), and setClockDelay().

| int nxyter::MainAdc::setClockDelaySrInit | ( | uint32_t | val | ) |

Set nXYTER to ADC clock phase, 'SR_INIT' part.

Low level method to setup one of of two parameters controling the relative phase between the nXYTER and the ADC clock. At the user level always call setClockDelay().

The 'SR_INIT' setting determines the initial value of the ADC-Clock generating shift register.

- Parameters:

-

val new initial shift register setting (16 bit)

- Returns:

- see roc::Board get/put/oper return codes

- See also:

- getClockDelaySrInit()

Definition at line 573 of file MainAdc.cxx.

References base::Peripheral::board(), CON19, fPort, isSPI(), base::Board::put(), ROC_NX_SR_INIT, and ROC_NX_SR_INIT2.

Referenced by cmd_scanadclat(), and setClockDelay().

| int nxyter::MainAdc::setRegister | ( | uint8_t | reg, | |

| uint8_t | val, | |||

| bool | veri = false | |||

| ) |

Write to ADC device register with optional readback verification.

Writes the 8bit value val to device register reg. If veri is true, the register contents is read back and verified.

- Parameters:

-

reg device register number val value veri if truereadback verification done (default isfalse)

- Returns:

- see roc::Board get/put/oper return codes

- See also:

- getRegister()

Definition at line 84 of file MainAdc.cxx.

References base::Peripheral::board(), fPort, isSPI(), base::Board::kOperBusErr, base::Board::operErrBuild(), base::Board::operGen(), ROC_NX_ADC_ADDR, ROC_NX_ADC_ADDR2, ROC_NX_ADC_ANSWER, ROC_NX_ADC_ANSWER2, ROC_NX_ADC_REG, and ROC_NX_ADC_REG2.

Referenced by cmd_setadc(), probe(), AdcWidget::regChanged(), AdcWidget::setSubConfig(), setTestMode(), setToDefault(), and setUserPattern().

| int nxyter::MainAdc::setTestMode | ( | int | ch, | |

| uint8_t | mode | |||

| ) |

Setup test pattern mode mode for ADC channel ch.

- Parameters:

-

ch ADC channel number (0-3) mode ADC test pattern mode (0-12)

- Returns:

- see roc::Board get/put/oper return codes

Definition at line 214 of file MainAdc.cxx.

References getRegister(), kReg_device_index_A, kReg_test_io, base::Board::operErrBuild(), and setRegister().

Referenced by cmd_setadcpatt(), and nxyter::FebUtil::testMainAdcDataPath().

| int nxyter::MainAdc::setToDefault | ( | ) |

Set the ADC registers to default values suitable for data taking.

Rewrite all ADC registers which determine operation to the power-up defaults. Only exception is the serial_control register, which is set for 12 bit operation (rather than nominal bitstream). This allows to use also 10 bit ADC's, some early FEB actually did so.

In particular:

- all test pattern modes are canceled, measured ADC values will transmitted (channel mask is first set to b1111, that the test_io register is set to 0)

- all channels are powered up

All writes are verified, so an error return is truely bad news.

- Returns:

- see roc::Board get/put/oper return codes

Definition at line 329 of file MainAdc.cxx.

References kReg_chip_port_config, kReg_clock, kReg_device_index_A, kReg_modes, kReg_output_adjust, kReg_output_mode, kReg_output_phase, kReg_serial_ch_stat, kReg_serial_control, kReg_test_io, base::Board::operErrBuild(), and setRegister().

Referenced by cmd_setadcdef(), AdcWidget::setSubToDefault(), and nxyter::FebBase::setToDefault().

| int nxyter::MainAdc::setUserPattern | ( | uint16_t | pat | ) |

Setup user test pattern pat for all ADC channels.

- Parameters:

-

pat user test pattern, 16 bits stored, lower 12 bits used

- Returns:

- see roc::Board get/put/oper return codes

Definition at line 236 of file MainAdc.cxx.

References kReg_user_patt1_lsb, kReg_user_patt1_msb, base::Board::operErrBuild(), and setRegister().

Referenced by cmd_setadcpatt(), and nxyter::FebUtil::testMainAdcDataPath().

Friends And Related Function Documentation

| std::ostream & operator<< | ( | std::ostream & | os, | |

| nxyter::MainAdc & | obj | |||

| ) | [related] |

ostream insertion for nxyter::MainAdc

Just calls nxyter::MainAdc::printRegisters()

Definition at line 89 of file MainAdc.h.

References printRegisters().

Field Documentation

base::Board* base::Peripheral::fBoard [protected, inherited] |

board pointer

Definition at line 26 of file Peripheral.h.

Referenced by base::Peripheral::board(), base::Peripheral::getBoard(), and base::Peripheral::Peripheral().

bool nxyter::MainAdc::fMode4nx [protected] |

int nxyter::MainAdc::fPort [protected] |

the port number

Definition at line 20 of file MainAdc.h.

Referenced by getAdcDirect(), getClockDelayBufg(), getClockDelaySrInit(), getRegister(), setClockDelayBufg(), setClockDelaySrInit(), and setRegister().

int nxyter::MainAdc::fUseSPI [protected] |

The documentation for this class was generated from the following files:

- include/nxyter/MainAdc.h (r4864/r4162)

- roclib/src_nxyter/MainAdc.cxx (r4864/r4162)

1.7.1

1.7.1